**School Of Engineering**

## **REMOTE AD HOC SENSOR NETWORKS**

Li-Wen Yip

Bachelor of Engineering in Computer Systems Engineering

# Thesis

October 2004

JAMES COOK UNIVERSITY

## SCHOOL OF ENGINEERING

## EG4010

Computer Systems Engineering

## **REMOTE AD HOC SENSOR NETWORKS**

Li-Wen Yip

Thesis submitted to the School of Engineering in partial fulfilment of the requirements for the degree of

**Bachelor of Engineering with Honours**

## (Computer Systems)

11 November 2005

## ABSTRACT

Australia's vast geographical expanses present challenging communications problems for data collection, which often require the use of high power radio links. Many of these scenarios lend themselves to the use of multi-hop ad hoc sensor networks, which can provide an alternative, more flexible and economical solution. However, little if any research has been conducted into developing network protocols suitable for these scenarios, which are characterised by remote and inaccessible locations, sparse topologies, and link ranges of up to 10 kilometres.

The first goal of this project was to develop a dynamic address allocation algorithm to realise the goal of zero configuration, with minimal energy overhead. The second goal was to develop an energy efficient media access control protocol, to maximise the battery life of each node.

The MAC protocol features a synchronised wakeup, which suits the periodic bulk data transfer typical of data logging applications. During inactive periods, a preamble sampling technique provides dramatic power savings whilst maintaining minimal network connectivity. The sampling frequency is dynamically optimised for maximum power savings, based on anticipated variations in local traffic levels.

The address allocation protocol is based on an existing technique, in which each node possesses a block of addresses. These addresses may be autonomously allocated to other nodes without distributed agreement, which results in a protocol with extremely low control overhead and minimal power consumption. This technique has been optimised to further reduce the control overhead for each operation, and avoid unnecessarily flooding the network with search requests.

A microcontroller based hardware platform was constructed, and was used to develop, implement and test the aforementioned protocols. The MAC protocol has been implemented and tested on the microcontroller, whilst the addressing protocol has been implemented in the ns-2 wireless network simulator. The design of the hardware platform has also been improved, improving energy efficiency and performance.

## ACKNOWLEDGEMENTS

I would like to express my sincere thanks to Mr John Wicking. Without his invaluable advice and direction, this thesis project would not have been possible. I would also like to thank the ECE technical staff, whose immeasurable knowledge, experience, and common sense have saved me from many headaches.

To my friends, for sharing in the insane antics which have helped me maintain my humanity and sense of humour throughout this year, and for reminding me that there is more to life than thesis.

Finally, to my family, for supporting and encouraging me through the greater part of my life.

## **STATEMENT OF ACCESS**

I, the undersigned, the author of this Thesis, understand that James Cook University will make the Thesis available for use within the University Library, by microfilm, or other means, and to allow access to users in other approved libraries.

All users consulting this Thesis will have to sign the following statement:

"In consulting this Thesis, I agree not to copy or closely paraphrase it in whole or in part without the written consent of the author; and to make proper public written acknowledgement for any assistance, which I have obtained from it."

Beyond this, I do not wish to place any restriction on access to this Thesis.

Li-Wen Yip

Date

## SOURCE DECLARATION

I declare that this Thesis is my own work and has not been submitted in any for another Degree or Diploma at any university or other institution of tertiary education. Information derived from the published or unpublished work of others has been acknowledged in the text and a list of references given.

Li-Wen Yip

Date

## TABLE OF CONTENTS

| Снарте | ER 1 INTRODUCTION                    | 1   |

|--------|--------------------------------------|-----|

| 1.1    | Background                           | 1   |

| 1.2    | Previous Work                        |     |

| 1.3    | Proposed Work                        | 3   |

| 110    |                                      | e e |

| Снарте | ER 2 RESEARCH                        | 4   |

| 2.1    | Power Conservation Techniques        | 4   |

| 2.1.1  | 1 On-Demand Wakeup                   |     |

| 2.1.2  | 2 Scheduled Rendezvous               | 5   |

| 2.1.3  | 3 Asynchronous Wakeup                | 7   |

| 2.1.4  | 4 Sleep Based Routing Extensions     | 9   |

| 2.1.5  | 5 Preamble Sampling                  |     |

| 2.1.6  | 6 Discussion                         |     |

| 2.1.7  | 7 Conclusions                        |     |

| 2.2    | Dynamic Address Assignment Protocols | 16  |

| 2.2.1  | 1 Introduction                       |     |

| 2.2.2  | 2 Decentralised Protocols            |     |

| 2.2.3  | 3 Leader-based Protocols             |     |

| 2.2.4  | 4 Hybrid Protocols                   |     |

| 2.2.5  | 5 Discussion                         |     |

| 2.2.0  | 6 Conclusions                        |     |

| Снарте | ER 3 DEVELOPMENT                     | 29  |

| 3.1    | Hardware Architecture                |     |

| 3.1.1  | 1 VGA Bypass Problem                 |     |

| 3.1.2  |                                      |     |

| 3.2    | Software Architecture                |     |

| 3.2.1  | 1 The OSI Model                      |     |

| 3.2.2  | 2 Relocatable Code                   |     |

| 3.3                                                                                     | Manchester Encoding and Decoding                                                                                                                                                                         |          |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.3                                                                                     | .1 Introduction                                                                                                                                                                                          |          |

| 3.3                                                                                     | .2 Manchester Encoding                                                                                                                                                                                   | 39       |

| 3.3                                                                                     | .3 Manchester Decoding and Synchronisation                                                                                                                                                               |          |

| 3.3                                                                                     | .4 Software Buffers                                                                                                                                                                                      |          |

| 3.4                                                                                     | Media Access Control                                                                                                                                                                                     | 50       |

| 3.4                                                                                     | .1 Preamble Sampling                                                                                                                                                                                     | 50       |

| 3.4                                                                                     | .2 Schedule Synchronisation                                                                                                                                                                              | 56       |

| 3.4                                                                                     | .3 Media Contention and Collision Management                                                                                                                                                             |          |

| 3.5                                                                                     | Address Allocation                                                                                                                                                                                       | 60       |

| 3.5                                                                                     | .1 Network Setup                                                                                                                                                                                         | 61       |

| 3.5                                                                                     | .2 Node Join                                                                                                                                                                                             | 61       |

| 3.5                                                                                     | .3 Local Allocation                                                                                                                                                                                      |          |

| 3.5                                                                                     | .4 Global Address Search                                                                                                                                                                                 | 64       |

| Снарт                                                                                   | ER 4 IMPLEMENTATION AND TESTING                                                                                                                                                                          | 66       |

|                                                                                         |                                                                                                                                                                                                          |          |

| 4.1                                                                                     | Hardware Platform                                                                                                                                                                                        | 66       |

| <b>4.1</b><br>4.1                                                                       |                                                                                                                                                                                                          |          |

| -                                                                                       | .1 Node PCB Design and Construction                                                                                                                                                                      |          |

| 4.1                                                                                     | .1 Node PCB Design and Construction                                                                                                                                                                      | 66<br>69 |

| 4.1<br>4.1                                                                              | <ul> <li>.1 Node PCB Design and Construction</li> <li>.2 ADG918 / ADG919 Wideband CMOS Switch</li> <li>Manchester Encoding and Decoding</li> </ul>                                                       |          |

| 4.1<br>4.1<br><b>4.2</b>                                                                | <ul> <li>.1 Node PCB Design and Construction</li></ul>                                                                                                                                                   |          |

| 4.1<br>4.1<br><b>4.2</b><br>4.2                                                         | <ol> <li>Node PCB Design and Construction.</li> <li>ADG918 / ADG919 Wideband CMOS Switch</li> <li>Manchester Encoding and Decoding.</li> <li>Manchester Encoding</li> <li>Manchester Encoding</li> </ol> |          |

| 4.1<br>4.1<br><b>4.2</b><br>4.2<br>4.2                                                  | <ul> <li>.1 Node PCB Design and Construction</li></ul>                                                                                                                                                   |          |

| 4.1<br>4.1<br><b>4.2</b><br>4.2<br>4.2<br>4.2                                           | <ul> <li>.1 Node PCB Design and Construction</li></ul>                                                                                                                                                   |          |

| 4.1<br>4.1<br>4.2<br>4.2<br>4.2<br>4.2<br>4.2<br>4.3                                    | <ol> <li>Node PCB Design and Construction</li></ol>                                                                                                                                                      |          |

| 4.1<br>4.1<br><b>4.2</b><br>4.2<br>4.2<br>4.2<br>4.2<br><b>4.3</b><br>4.3               | <ol> <li>Node PCB Design and Construction</li></ol>                                                                                                                                                      |          |

| 4.1<br>4.2<br>4.2<br>4.2<br>4.2<br>4.2<br>4.2<br>4.2<br>4.3<br>4.3<br>4.3               | <ol> <li>Node PCB Design and Construction</li></ol>                                                                                                                                                      |          |

| 4.1<br>4.1<br>4.2<br>4.2<br>4.2<br>4.2<br>4.2<br>4.2<br>4.3<br>4.3<br>4.3<br>4.3        | <ol> <li>Node PCB Design and Construction</li></ol>                                                                                                                                                      |          |

| 4.1<br>4.1<br>4.2<br>4.2<br>4.2<br>4.2<br>4.2<br>4.2<br>4.3<br>4.3<br>4.3<br>4.3<br>4.3 | <ol> <li>Node PCB Design and Construction</li></ol>                                                                                                                                                      |          |

| 4.4.3      | Design                           |

|------------|----------------------------------|

| 4.4.4      | Implementation                   |

| CHAPTER 5  | DISCUSSION OF RESULTS            |

| 5.1.1      | Hardware Architecture            |

| 5.1.2      | Manchester Encoding and Decoding |

| 5.1.3      | MAC Protocol                     |

| 5.1.4      | Address Allocation Protocol      |

| CHAPTER 6  | CONCLUSION93                     |

| CHAPTER 7  | CONTINUATIONS AND EXTENSIONS     |

| 7.1 Soft   | ware Simulation                  |

| 7.2 Loc    | ation Discovery                  |

| Reference  | s97                              |

| APPENDIX A | SOFTWARE FLOW CHARTS 101         |

| A.1 Enc    | oding and Decoding101            |

| A.2 Add    | lress Allocation 106             |

| Appendix E | SCHEMATIC DIAGRAMS 115           |

| APPENDIX C | С Raw Data 117                   |

| Appendix D | NS-2 SIMULATION SOFTWARE 118     |

| APPENDIX E | MICROCONTROLLER SOFTWARE LISTING |

| E.1 Hea    | der Files 126                    |

| E.2 Mod    | dules134                         |

| E.3 Peri   | pherals                          |

## LIST OF FIGURES

| Figure 2.2 - Sleep/Wake Cycles [9]7                                                                   |

|-------------------------------------------------------------------------------------------------------|

|                                                                                                       |

| Figure 2.3 - Beacons in the absence of slot boundary alignment [5]8                                   |

| Figure 2.4 - A SPAN network with 100 nodes and 19 coordinators [10]9                                  |

| Figure 2.5 - Preamble Sampling11                                                                      |

| Figure 3.1 - 2004 Hardware Block Diagram                                                              |

| Figure 3.2 - Emitter Follower Voltage Sources                                                         |

| Figure 3.3 - The 7 Layers of the OSI Model [36]                                                       |

| Figure 3.4 - Generating Executable Code from Object Modules [37]37                                    |

| Figure 3.5 – Manchester Encoding                                                                      |

| Figure 3.6 - Manchester Clock Drift                                                                   |

| Figure 3.7 - No Clock Drift40                                                                         |

| Figure 3.8 – RxD with no signal present; 5V/div; 1ms/div42                                            |

| Figure 3.9 - Repeated framing errors                                                                  |

| Figure 3.10 - Synchronous logic decoding process                                                      |

| Figure 3.11 - Edge capture / sampling timing diagram                                                  |

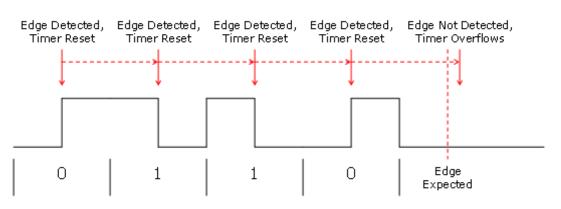

| Figure 3.12 - Clock Detection Timing Diagram                                                          |

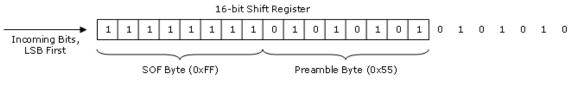

| Figure 3.13 - Start of Frame Detection                                                                |

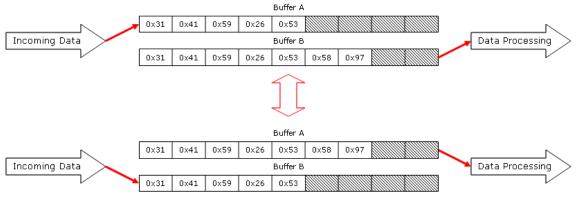

| Figure 3.14 - Popcorn Buffering                                                                       |

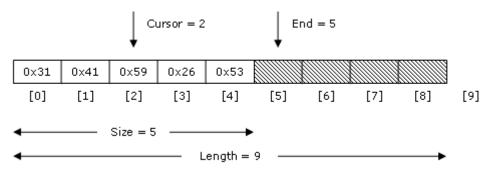

| Figure 3.15 - Buffer Data Structure                                                                   |

| Figure 3.16 - Buffer Data Structure Memory Map49                                                      |

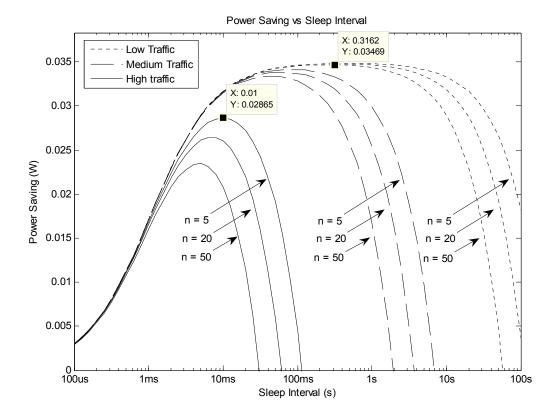

| Figure 3.17 - Power Saving vs. Sleep Interval54                                                       |

| Figure 3.18 - Carrier Detect (Active Low), No signal present, 5V/div, 1ms/div59                       |

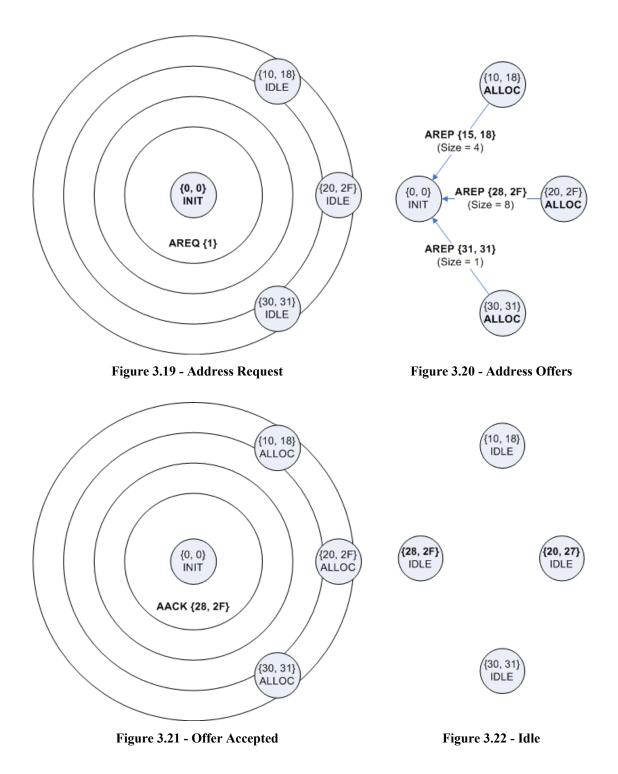

| Figure 3.19 - Address Request                                                                         |

| Figure 3.20 - Address Offers                                                                          |

| Figure 3.21 - Offer Accepted                                                                          |

| Figure 3.22 - Idle                                                                                    |

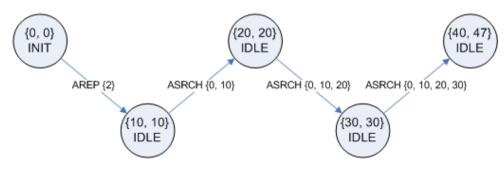

| Figure 3.23 - ASRCH message contains a routing information                                            |

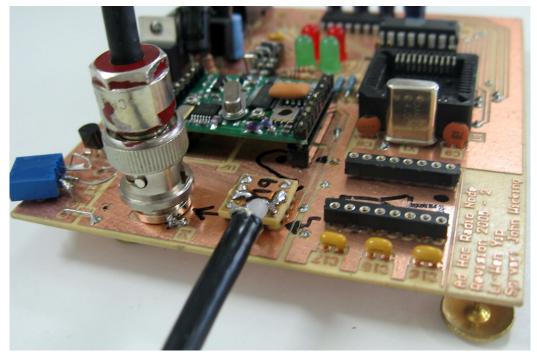

| Figure 4.1 - Ad hoc radio node PCB; Revision 3 as constructed                                         |

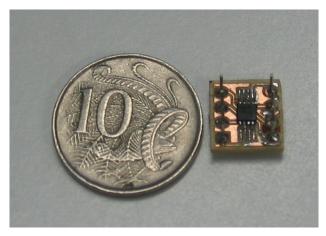

| Figure 4.2 - ADG918/ADG919 Carrier Board71                                                            |

| Figure 4.3 - Carrier board soldered directly to PCB; Coaxial cable soldered directly to carrier board |

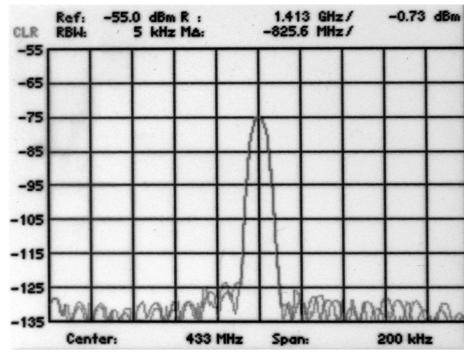

| Figure 4.4 - Signal strength in ON state (-75dBm)72                                                   |

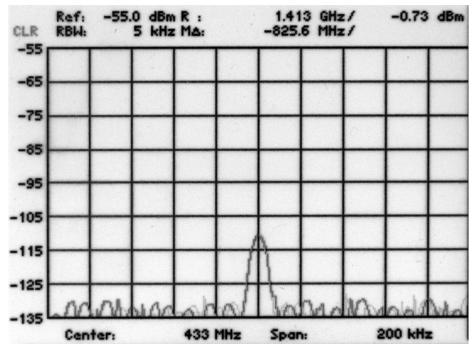

| Figure 4.5 - Signal strength in OFF state (-110dBm)                 | 72  |

|---------------------------------------------------------------------|-----|

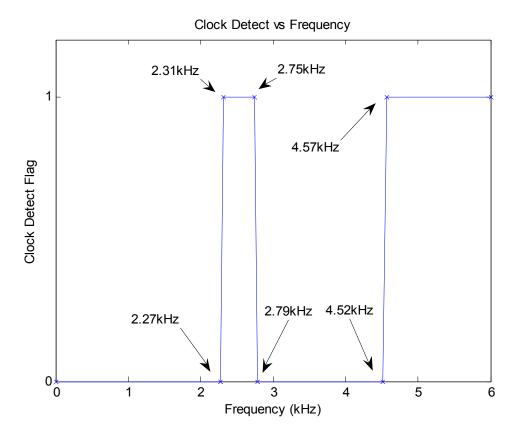

| Figure 4.6 - Clock Detect Flag vs. Frequency                        | 77  |

| Figure 4.7 - Message successfully received (The answer is 42!)      | 79  |

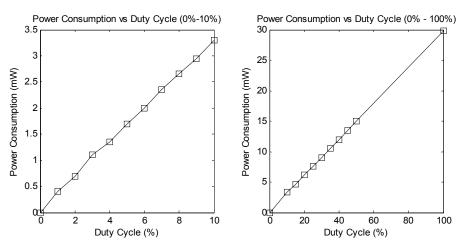

| Figure 4.8 - Power Consumption vs. Duty Cycle for X2010 Transceiver | 81  |

|                                                                     |     |

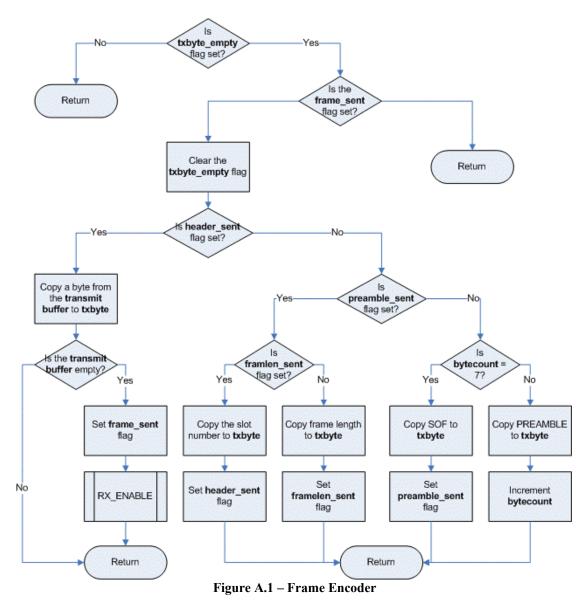

| Figure A.1 – Frame Encoder                                          |     |

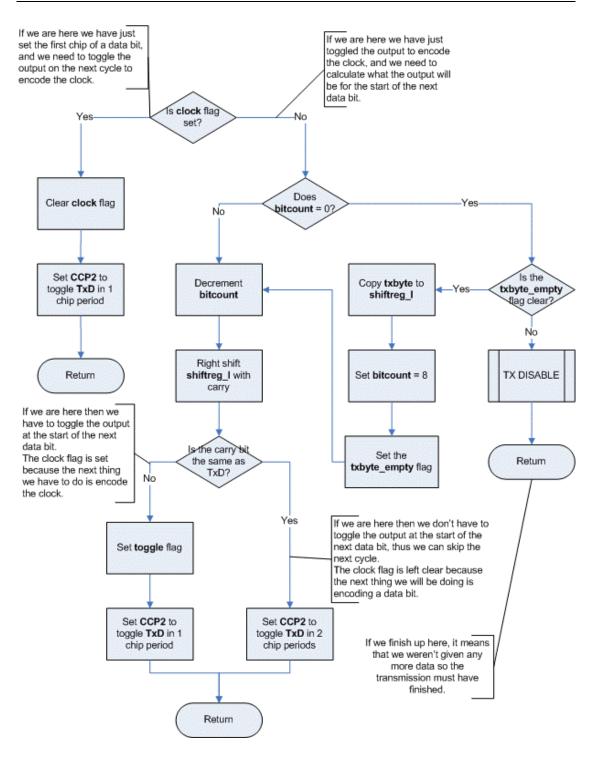

| Figure A.2 - Manchester Encoder                                     |     |

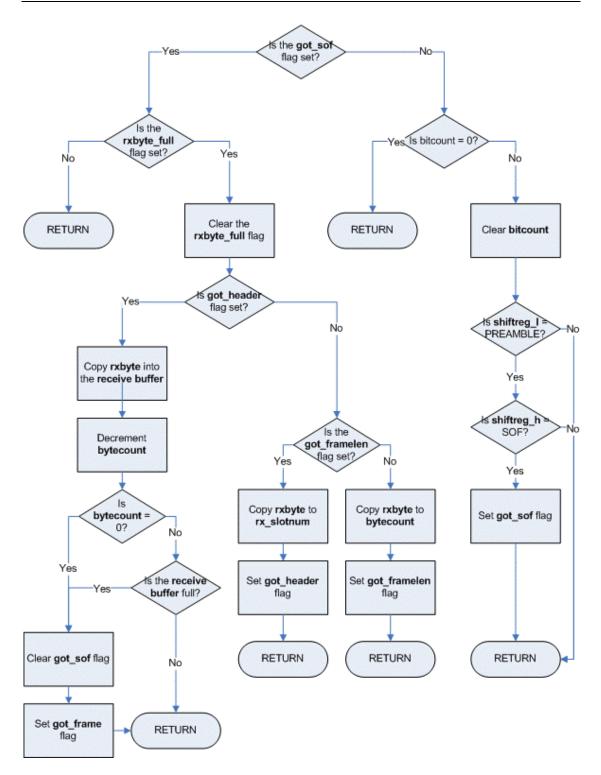

| Figure A.3 - Frame Decoder                                          | 103 |

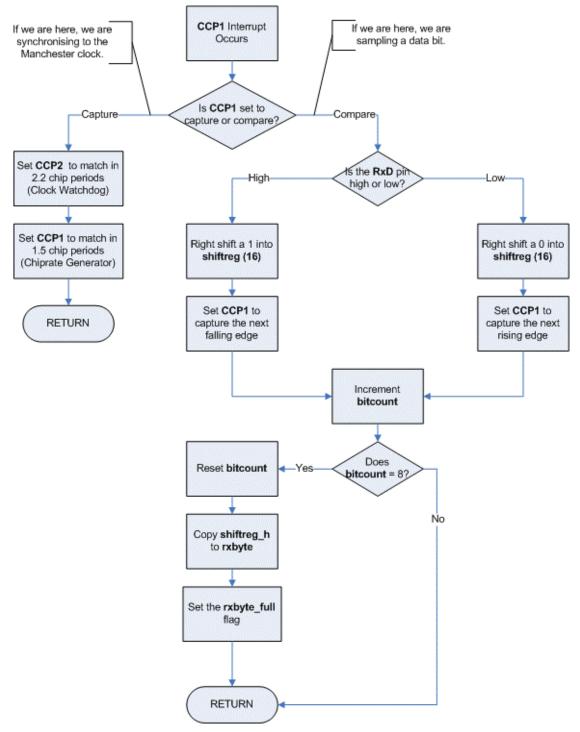

| Figure A.4 - Manchester Decoder                                     | 104 |

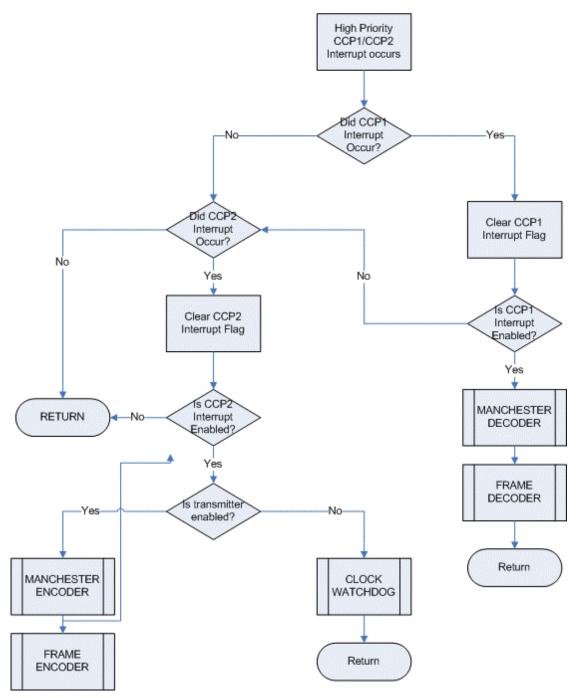

| Figure A.5 - High Priority Interrupt Service Routine                |     |

| Figure A.6 - Node Startup Event                                     |     |

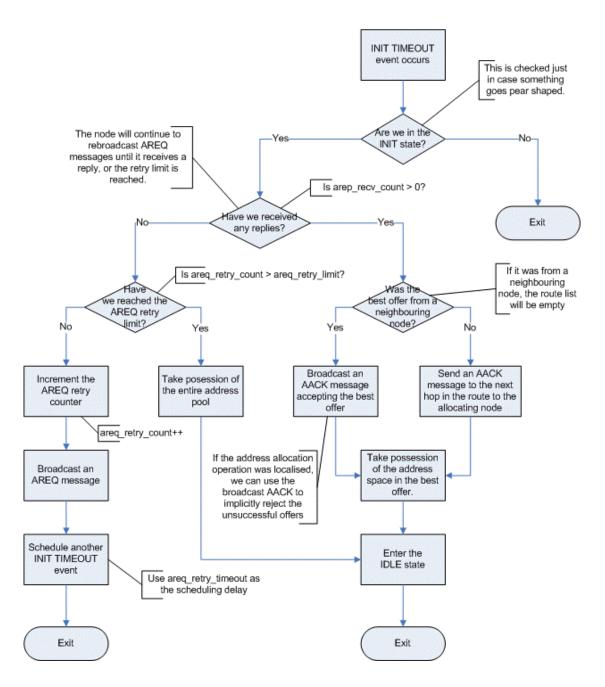

| Figure A.7 - Initialisation Timeout Event                           | 107 |

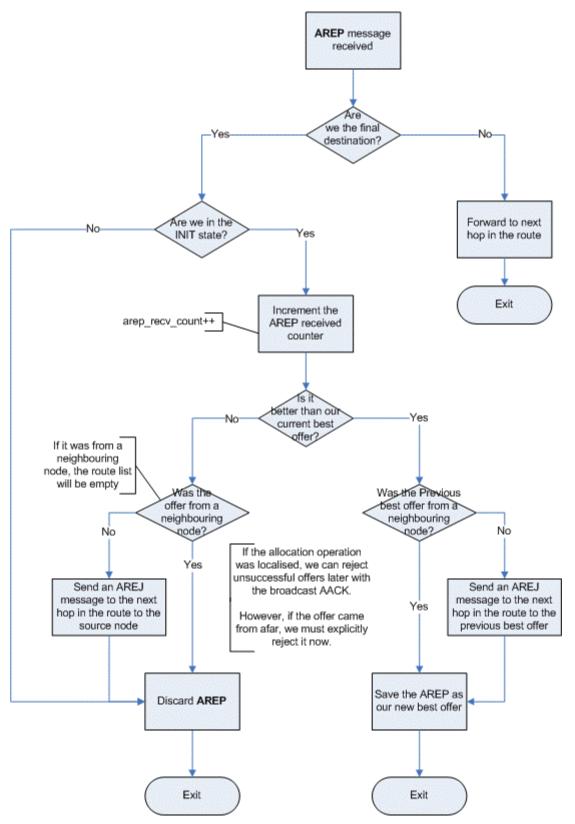

| Figure A.8 - AREP Message Received Event                            |     |

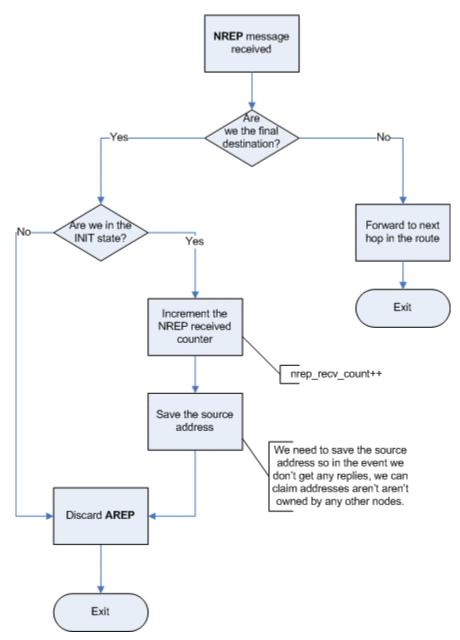

| Figure A.9 - NREP Message Received Event                            |     |

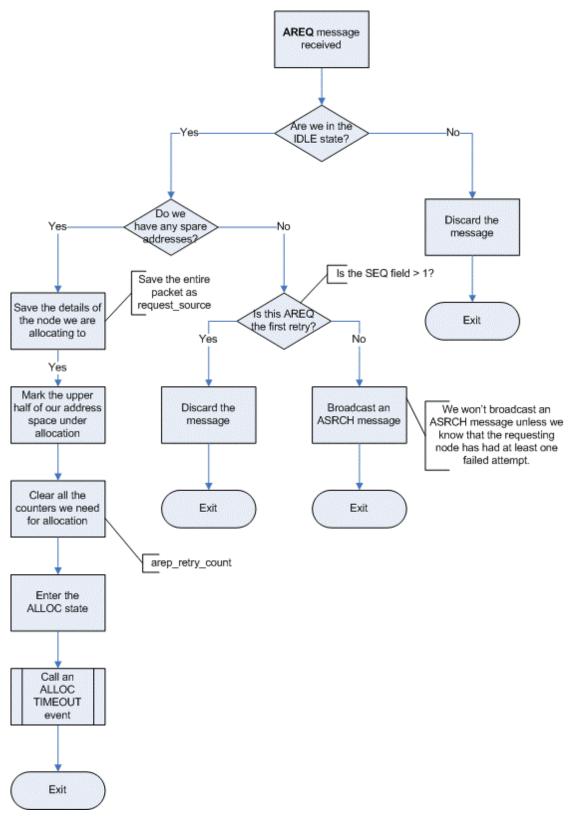

| Figure A.10 - AREQ Message Received Event                           | 110 |

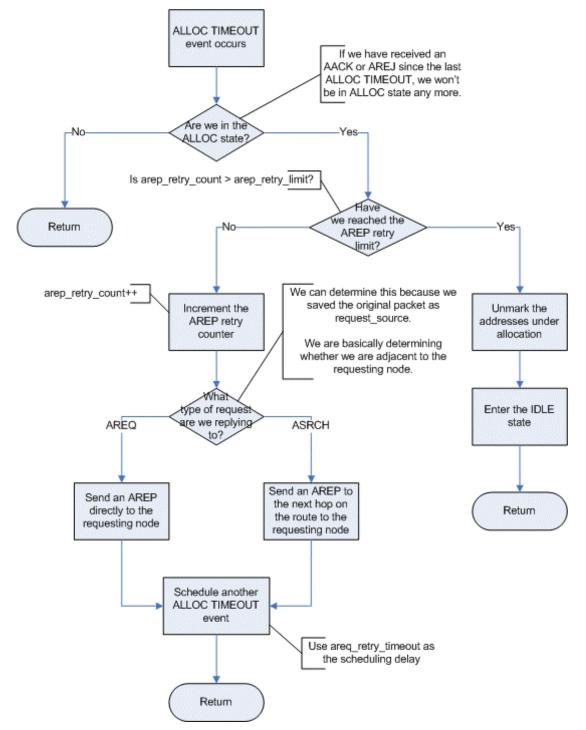

| Figure A.11 - Allocation Timeout Event                              | 111 |

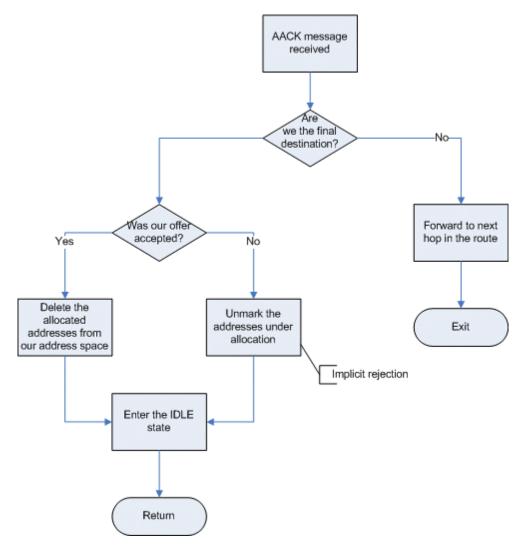

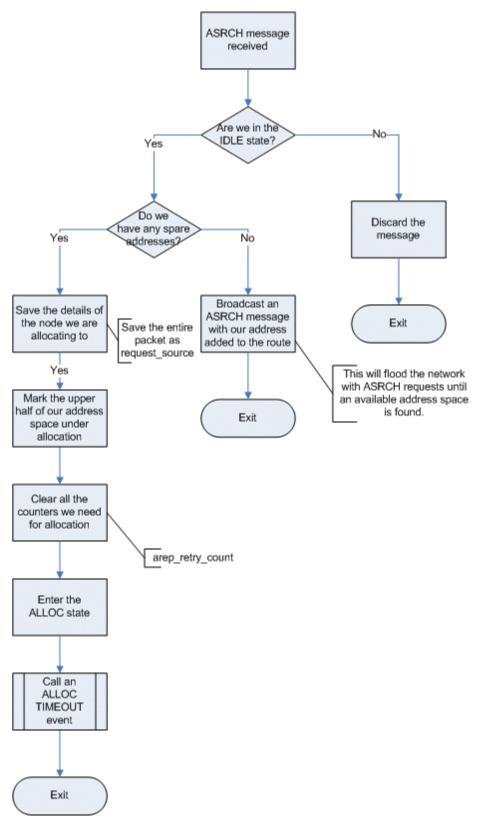

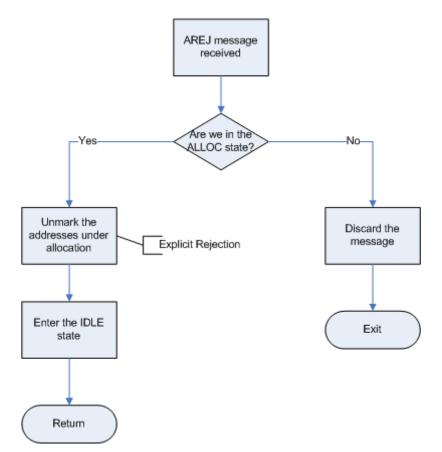

| Figure A.12 - AACK Message Received Event                           | 112 |

| Figure A.13 - ASRCH Message Received Event                          | 113 |

| Figure A.14 - AREJ Message Received Event                           | 114 |

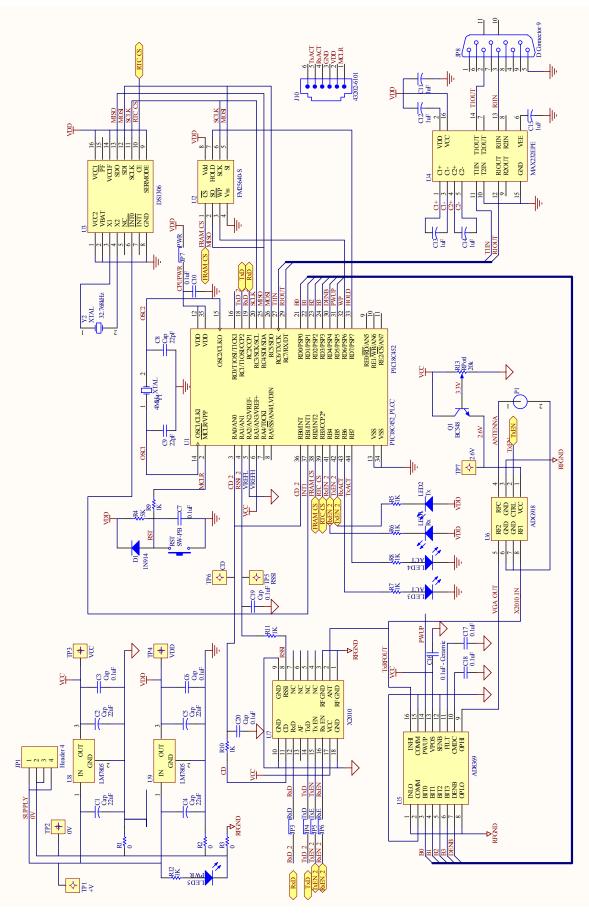

| Figure B.1 - Node Rev 3 Schematic Diagram                           | 116 |

## LIST OF TABLES

| Table 3.1 - Classification of traffic rates                   | 53  |

|---------------------------------------------------------------|-----|

| Table 3.2 - Hardware Parameters                               | 53  |

| Table 4.1 - Instruction Cycles for Encoding Operations        | 75  |

| Table 4.2 - Frequency and Duty cycle measurements             | 75  |

| Table 4.3 - Byte Waveforms                                    | 76  |

| Table 4.4 - Instruction Cycles for Decoding Operations        |     |

| Table 4.5 - Definition of Packet                              |     |

| Table 4.6 - Definition of Node                                | 87  |

|                                                               |     |

| Table C.1 - X2010 Transceiver Power Consumption vs Duty Cycle | 117 |

| Table D.1 - DAA.H                                             | 118 |

| Table D.1 - DAA.CC                                            |     |

| Table E.1 - MACROLIB.INC                                      |     |

| Table E.2 - PINCONNECTIONS.INC                                |     |

| Table E.3 - SWSTACK.INC                                       | 130 |

| Table E.4 - BUFFERS.INC                                       | 131 |

| Table E.5 - MAIN.ASM                                          |     |

| Table E.6 - PHY.INC                                           | 137 |

| Table E.7 - PHY.ASM                                           | 137 |

| Table E.8 - MAC.INC                                           | 145 |

| Table E.9 - MAC.INC                                           | 145 |

| Table E.10 - SPI.ASM                                          |     |

| Table E.11 - RTC.INC                                          |     |

| Table E.12 - RTC.ASM                                          |     |

| Table E.13 - ROUTECACHE.ASM                                   | 167 |

| Table E.14 - SWTIMERS.ASM                                     | 174 |

|                                                               |     |

## Chapter 1

## INTRODUCTION

#### **1.1 BACKGROUND**

Ad hoc networking is currently a very active area of research at many institutions around the world. A subclass of ad hoc networks are *ad hoc sensor networks*, which are typically characterised by long battery life, low traffic rates, low power radios, and dense, well connected topologies. The sensor nodes integrate data collection, data processing and communications functions into a tiny package with long battery life.

There are several existing projects which are at an advanced level of development, including Berkley University Smart Dust, Crossbow Motes, and the TinyOS operating system. There have also been numerous publications presenting new protocols and techniques for media access control, power management, routing, and address allocation. However, little or no research has been specifically conducted into ad hoc sensor networks which feature sparse, minimally connected topologies, and a large geographical distance between nodes. The target application is an ad hoc radio network for environmental monitoring stations on the Great Barrier Reef, which will allow data to be collected and relayed back to the Australian Institute of Marine Sciences at Cape Cleveland. This data is currently collected by high power / long range radio links, which requires expensive and bulky batteries and radios, as well as a costly radio license.

The sparse topology, remote location, and typically harsh environmental conditions present a new set of challenges, including vulnerability to the elements, varying link quality, multi-path propagation, poor SNR and interference, propagation delays, and low maintenance requirements. This scenario requires a different set of techniques and protocols to achieve the desired goals of minimal power consumption, zero configuration and planning, dynamic reconfiguration, and reliable connectivity.

#### **1.2 PREVIOUS WORK**

This thesis project was started in 2003 by Nigel Sim [1], who researched a very broad range of topics related to ad hoc networking. The primary focus of this work was developing a simulation environment written in Python. Several basic protocols were developed, implemented, and tested in this simulation environment, operating atop both a microprocessor based physical layer and a software simulated physical layer.

Steven Sloots [2] continued this work in 2004, focussing his efforts on developing an energy efficient routing protocol. A dynamic source routing (DSR) based protocol was developed, and modified to distribute routing information over the entire route to reduce the size of the network header and associated energy overhead. A power aware routing optimisation (PARO) was implemented, which dynamically modifies routes and transmission powers to minimise the energy cost of each route. The hardware, physical, and data link layers were also redesigned based on recommendations made by Sim.

#### **1.3 PROPOSED WORK**

The goal of this ongoing project is to develop a complete system which can be deployed on the Great Barrier Reef. With this in mind, several areas of work were identified which were required to move closer to this goal:

- Development and implementation of a media access control protocol which conserves energy by placing the nodes' radio transceivers in 'sleep' mode.

- 2. Development and implementation of a dynamic address allocation protocol, with primary goals of zero configuration and minimal power consumption.

- 3. Improvement of existing hardware and software where opportunities exist to improve efficiency, power consumption, or performance.

## Chapter 2

## RESEARCH

#### 2.1 **POWER CONSERVATION TECHNIQUES**

A primary concern in this project is to minimise the power consumption of each node, so as to obtain the longest possible battery life, reducing maintenance requirements. Steven Sloots [2] addressed this problem at the network layer by developing a power aware routing protocol, which dynamically adjusts routes and transmission powers to minimise the total energy cost of each route.

Research has shown that the energy required to monitor the medium for activity is only slightly less than that required for active communications [3]. This is supported by the specifications for the X2010 transceiver currently employed in this project: The nominal supply current is 7 mA in receive mode, 8 mA in transmit mode, and merely 1  $\mu$ A in sleep mode [4]. Network traffic in ad hoc sensor networks is typically very low, thus significant power savings can be made by placing the nodes' radios in sleep mode. This technique is typically implemented as a media access control protocol or routing extension which operates the nodes' radios on a low duty cycle, to minimise the amount of energy wasted monitoring the channel for activity. The role of such a protocol is to determine which nodes place their radios into sleep mode, and when [5].

Power conservation in ad hoc networks is currently a very active area of research, and as such there are a plethora of existing protocols. As it would be impossible to research every existing protocol, the remainder of this section will discuss various techniques, and some of their more prominent protocol implementations.

#### 2.1.1 On-Demand Wakeup

In on-demand wakeup, nodes may sleep until they are woken up by another node which wishes to communicate with it. This is typically facilitated by a secondary radio device, which can much more efficiently monitor its channel for activity due to reduced complexity requirements. Systems used for the secondary radio include RFID [6], and low power ISM band radios [7]. However, this introduces additional hardware requirements, which add to the size and cost of each node. Of greater concern is that the secondary radio must operate over the same range as the primary radio [5]. This is a particular problem in a long range ad hoc network, where distances between nodes are up to 10km. As such, this technique is not applicable to this project.

#### 2.1.2 Scheduled Rendezvous

A scheduled rendezvous protocol is one in which nodes' sleep schedules are synchronised, such that there is a communication window where all nodes are monitoring the medium. One of the problems with this technique is that adjacent nodes which have non-overlapping sleep schedules may never discover each other [5]. Another problem discussed in [5] is that this technique is not suitable for multi-hop ad hoc networks, as distributed clock synchronisation is difficult to achieve. However, this technique would be implemented at the link layer, thus clock synchronisation is only necessary between adjacent nodes.

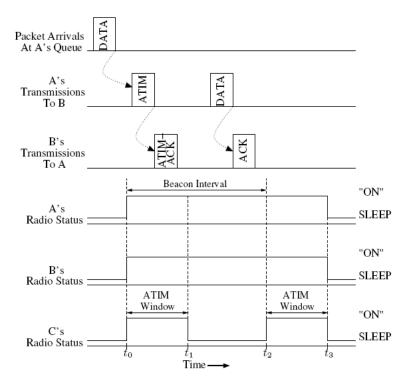

#### 2.1.2.1 <u>802.11b IBSS Power Saving Mode</u>

In 802.11b IBSS Power Saving Mode [8], synchronisation is facilitated by having nodes contend to transmit the synchronisation beacon with backoff. These beacons signal the start of a window used exclusively for handshaking, known as an *ad hoc traffic indication message (ATIM) Window*. Data packets are exchanged in the intervals between the ATIM windows. During the ATIM window, nodes which wish to communicate exchange ATIM messages and acknowledgements (Figure 2.1). Once the window has elapsed, nodes which sent or received ATIM messages remain awake to exchange packets, whilst all other nodes return to sleep.

Note that this protocol in its original form is not suited for multi-hop ad hoc networks, as the synchronisation mechanism will not work unless all nodes in the network can hear each other.

Figure 2.1 - IEEE 802.11 IBSS Power Save Mode [8]

#### 2.1.3 Asynchronous Wakeup

An asynchronous wakeup protocol is one in which nodes' wakeup schedules are not synchronised, instead relying on the schedules of neighbouring nodes overlapping to create a communication window for those two nodes.

#### 2.1.3.1 <u>Contiguous Wakeup Schedule</u>

Feeney [9] has developed an asynchronous protocol where each sleep cycle has a single contiguous "on" period, and a duty cycle of more than 50%. Therefore, neighbouring nodes' sleep schedules are guaranteed to overlap without requiring any synchronisation.

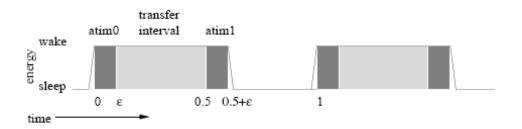

Each wake interval is divided into two ATIM windows and one transfer interval, as indicated in Figure 2.2. At least one of the ATIM windows is guaranteed to fall within the wake interval of each neighbouring node. During the ATIM period, nodes which wish to communicate exchange messages which allow them to estimate their phase difference, and if necessary adjust their phase to increase the amount of overlap to accommodate higher traffic. The ATIM windows are also used for broadcast and multicast traffic, although a broadcast message must be transmitted in both ATIM windows to guarantee that it will be received by all adjacent nodes.

The fundamental limitation of this approach as noted by the author is that each node must be awake for at least fifty percent (50%) of the time.

Figure 2.2 - Sleep/Wake Cycles [9]

#### 2.1.3.2 Arbitrary Wakeup Schedule

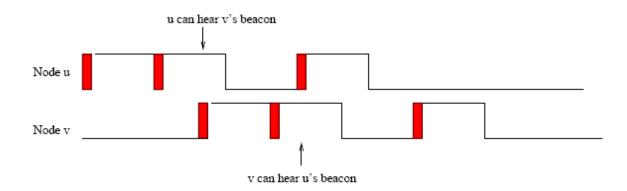

Zheng et al [5] have developed a protocol in which each node's sleep cycle is divided into a number of slots, each of which may be an "on" slot or a "off" slot. The authors demonstrate that for a cycle of a particular slot length, there exists an optimal *wakeup schedule function* which guarantees at least one slot overlap between any two nodes regardless of phase difference, provided that the slot boundaries are aligned. The authors go on to demonstrate that if the slot boundaries are not aligned, neighbours are guaranteed to detect each other's beacons transmitted at the start of each "on" slot (Figure 2.3). These beacons include information that allows other nodes to calculate the sender's schedule relative to their own, and when their schedules overlap. Outgoing packets are buffered, and transmitted when both sender and receiver are awake.

This protocol overcomes the limitation of [9] that limits the duty cycle to at least 50%. The authors give an example in which the wakeup schedule function has 73 slots, of which only 9 are "on" slots – a duty cycle of 12.3%.

However, like [9], a single message cannot be guaranteed to reach all adjacent nodes. The options for broadcasting would be to broadcast the message immediately after each beacon, or to unicast the message to all known neighbours.

Figure 2.3 - Beacons in the absence of slot boundary alignment [5]

#### 2.1.4 Sleep Based Routing Extensions

Several routing extensions have been developed based on the observation that there are several possible routes for a given source and destination. These protocols operate by allowing nodes which are redundant for routing purposes to conserve more power.

#### 2.1.4.1 <u>SPAN</u>

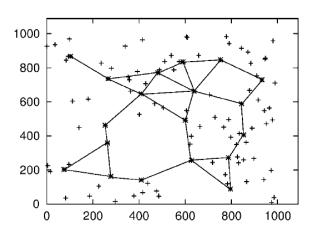

In SPAN [10], "coordinator" nodes remain awake to buffer and relay packets for other nodes, forming a low-latency backbone for the network. Other nodes are thus able to operate in an asynchronous low power mode. Each node decides individually whether to become a coordinator, based on how much energy it has available, and how much energy will be saved by its neighbours. The role of coordinators is periodically rotated, such that power savings are distributed equally to all nodes.

The salient features of SPAN include improved QoS due to the formation of a backbone; however this is not important in an ad hoc sensor network. The authors also note that this technique is only useful for a minimum node density; thus it is not applicable to sparse or long range ad hoc sensor networks. This also applies to other similar protocols based on the concept of a dominating set of nodes.

Figure 2.4 - A SPAN network with 100 nodes and 19 coordinators [10]

#### 2.1.4.2 Basic Energy Conservation Algorithm (BECA)

In *BECA* [11], idle nodes asynchronously alternate between listening and sleeping states. If a node either transmits or receives a packet, it transitions to an active state for a predetermined timeout. Whilst a node is active it continuously monitors the medium in anticipation of further network activity. The active timeout is set to be slightly longer than the retry interval for network level requests (e.g. RREQ and AREQ messages), so that involved nodes will remain active until the operation is complete. The sleep interval is set to be an integer multiple k of the network level retry interval, which guarantees that a sleeping node will be woken after k + l retries.

#### 2.1.4.3 <u>Adaptive Fidelity Energy Conservation Algorithm (AFECA)</u>

AFECA [11] is an extension of BECA which uses information about the local node density to dynamically modify sleep schedule duty cycles. The number of redundant routes for a particular source and destination increases with the node density, thus the duty cycle of nodes in a high density area can be decreased whilst maintaining a constant amount of routing redundancy.

As with SPAN, this technique has limited usefulness in sparse networks.

#### 2.1.5 Preamble Sampling

#### Figure 2.5 - Preamble Sampling

Preamble sampling (Figure 2.5) is an asynchronous technique which can be considered as an on-demand wakeup mechanism, as it uses the packet preamble to wake up sleeping nodes. Nodes periodically wake up to check for a wakeup signal (i.e. preamble). If a wakeup signal is detected, the node remains awake to receive the rest of the packet.

For a node to be woken up regardless of the phase of its wakeup schedule, the preamble must be at least the same length as one sleep cycle [12-15]. Therefore, the power savings made by the receiving node are partially offset by the energy required to transmit and receive the longer preamble.

El-Hoiydi [13] models the performance of preamble sampling when used in conjunction with Aloha [16] and CSMA [8] contention protocols, assuming fixed node densities and packet lengths. However, these results are not very useful, as they are more oriented towards optimising packet latency and throughput

Hill and Culler [15] demonstrate that by quickly measuring the energy in the channel to detect the wakeup signal, the awake interval can be reduced to 50  $\mu$ s, and the wakeup signal is reduced to a long RF pulse. Conversely, if the start of frame

sequence is used as a wakeup signal, the required awake interval is up to two packet lengths, or 108 ms at 10 kbps.

WiseMAC [14], developed by El-Hoiydi and Decotignie is a preamble-sampling based protocol designed for the downlink of infrastructure wireless sensor networks. It is similar to the downlink of 802.11b BSS Power Saving Mode [8], in that the access point learns the sampling schedules of each node and hence is able to minimize the length of its packet preambles. This also has the advantage of minimizing overhearing of packets by nodes which are not the intended recipients.

B-MAC [12], developed by Polastre et al. uses adaptive preamble sampling to reduce the duty cycle for optimal power savings. However, reconfiguration is controlled by protocols and services running at higher layers. For example, this allows network layer information to be used in the decision to reconfigure, such as whether a reply is expected to the packet just sent.

#### 2.1.6 Discussion

To determine the best approach to take toward designing a media access control protocol for this project, it is worthwhile to consider the typical deployment scenario for this type of network.

The nodes will typically be very sparse, with minimal connectivity, although there may be small clusters of nodes situated on reefs. The distance between adjacent nodes may be up to 10km, thus RF amplification will be used for transmission, which will make the energy cost of transmission significantly higher than that of receiving / listening. The traffic rates will be very low, with most activity occurring as a result of network layer operations (e.g. route discovery and address allocation) and data retrieval. Data retrieval will comprise every sensor node routing logged data back to a single *sink* node, which will occur at regular and predetermined intervals. Any MAC layer protocol also has to work in conjunction with the DSR/PARO routing protocol previously implemented by Sloots [2].

The last point is particularly important, as the PARO routing extension relies on nodes being able to overhear packets not intended for them. Therefore, both asynchronous protocols discussed [5, 9] would not be suitable, as they prevent overhearing of messages by non-involved nodes. Additionally, neither protocol supports an efficient broadcasting method. Due to the increased energy cost of transmissions, [9] is slightly better in that it only requires beacons to be transmitted when there is an impending packet transmission, however [5] requires periodic transmission of beacons.

The minimal connectivity of the network would mean that there would be very little routing redundancy, severely limiting the usefulness of both routing extensions discussed [10, 11]. Additionally, both would interfere with the PARO extension previously implemented in this project [2].

This means that the power save protocol should be based on either scheduled rendezvous, or preamble sampling. In fact, a combination of the two techniques may be useful, as follows in the conclusion.

#### 2.1.7 Conclusions

Recall that the majority of network traffic will be caused by either network level operations or transfer of data from sensors nodes to the sink node. Since a reactive routing protocol is used, route requests will only occur when there are impending data packets. Therefore, the only network traffic which will not occur on a predictable schedule is as a result of addressing operations, which mostly occur when the network is initially deployed.

Consider an example, where data is collected from sensor nodes once every six hours, and that data collection can be completed in one minute. Therefore, if a network-wide rendezvous is scheduled for one minute every six hours, the duty cycle of the system is reduced to approximately 0.28%, with no detrimental effects on packet latency or throughput.

Synchronizing the clocks of adjacent nodes to within one second is a non-trivial problem, and the propagation of synchronisation messages can be initiated by the sink node. However, having such a long sleep interval makes it impossible for asynchronous network operations to occur during this period, including address allocation and the initial synchronisation of nodes.

A possible solution is instead of defining global "awake" and "sleep" periods, define periods as "high traffic" and "low traffic" respectively. A preamble sampling technique can be used during the low traffic periods. Communication during these periods will be more energy expensive due to the increased preamble length; however the network is able to retain minimal connectivity. By using adaptive techniques to anticipate network activity similar to those used in [11, 12], the preamble energy overhead during the power save interval could be significantly reduced for network operations such as address requests.

For example, when an initialising node sends an address request, the network layer may instruct the MAC layer to wait the duration of the retry interval before reverting to power save mode, and instruct the MAC layer in neighbouring nodes not to use the extended preamble.

Moreover, the energy sampling technique used in [15] is equally applicable to the X2010 transceiver currently employed in this project. The X2010 data sheet [4] shows that the time from power up required to obtain a valid data is 5 ms, whereas the time required to obtain a valid RSSI reading is only 1ms. These concepts will be further developed in section 3.4 (p. 50).

#### 2.2 DYNAMIC ADDRESS ASSIGNMENT PROTOCOLS

#### 2.2.1 Introduction

Automatic configuration is a desirable feature for any system, as it eliminates the need for a skilled technician to assist with the deployment. One of the important functions of automatic configuration is *dynamic address assignment*, also known as *dynamic address allocation*, or simply *dynamic addressing*. Dynamic addressing refers to the process by which nodes automatically obtain a routable address upon joining a network. This is as opposed to static addressing, whereby a node is manually configured with an address before it joins a network. Dynamic addressing has many advantages over static addressing:

- 1. Automatic configuration allows easy deployment.

- 2. Allows nodes to move freely between networks.

- 3. Allows addresses to be recycled if the corresponding nodes have left the network.

- 4. It can cope with the dynamic nature of ad hoc networks.

In traditional TCP/IP networking, dynamic addressing is achieved exclusively with the ubiquitous *Dynamic Host Configuration Protocol* (DHCP), however the lack of static infrastructure in an ad-hoc network precludes its use. The following sections shall go on to investigate existing research into developing dynamic addressing protocols for ad hoc networks.

#### 2.2.1.1 Ad Hoc Network Dynamics

Ad hoc networks are of a very dynamic nature, with constantly changing network conditions, which the dynamic addressing protocol must have mechanisms to deal with. The changes that may occur can be classified into five distinct network events:

- Network creation an unconfigured node creates a new network, in the event that it cannot find any existing networks within communication range.

- 2. Node join An unconfigured node joins the network. The protocol must ensure that a unique address is allocated to the node.

- 3. Node part A node leaves the network. The protocol must ensure the release of the node's address to make it available for reallocation.

- Network partition The network is split into two parts either by a broken link or crashed node. The protocol must ensure that each partition is still able to continue operating as an independent network.

- 5. Network merge Nodes from two independent networks come within communication distance of each other. The protocol must detect and eliminate duplicate addresses to allow the two networks to be merged.

#### 2.2.1.2 Objectives

Sun and Belding Royer [17] list the following objectives for an ad hoc network dynamic address assignment protocol:

- 1. Dynamic Address Configuration Addresses are allocated without manual or static configuration.

- 2. Unique Address Allocation Each node is allocated a network-unique address.

- 3. Robustness The protocol should have mechanisms to deal with network merges and partitions.

- 4. Scalability The protocol should be applicable to networks of varying sizes without an adverse impact on its performance. The relevant performance metrics include timely address allocation, and minimal control overhead during address allocation.

The intended application of this thesis project is the monitoring of remote and inaccessible outdoor locations. Such a network would comprise sparsely distributed nodes, with inter-node hops of up to several kilometres. A likely scenario is that the nodes will be deployed in fixed locations, and network maintenance will consist of replacing nodes whose batteries have expired.

Therefore, the primary goal is to minimise the need for network maintenance by minimising the power consumption of the network. The largest consumer of energy in an ad hoc network is radio communications [18], especially in sparse networks where energy consumption is a function of the distance squared. Pottie and Kaiser [19] illustrate this concept with an example, where transmitting 1 kilobyte of data a distance of 100m uses the same amount of energy as performing 3 million instructions in a 100MIPS/W processor.

There are two ways in which the addressing algorithm can reduce the power consumption of the network:

- 1. *Minimise the control overhead of network operations*. This may be achieved by reducing the number of packets that must be transmitted to complete a network operation.

- 2. *Minimise the network addressing overhead*. Network addresses are transmitted in the network header of every packet transmitted, introducing network overhead, and associated energy consumption. This overhead may be significantly reduced by limiting the address space [20].

#### 2.2.1.3 <u>Classification of Address assignment protocols</u>

The address assignment protocols developed to date may be divided into three classifications according to their fundamental concept of operation:

- 1. *Decentralised* protocols, in which no one node has definitive knowledge of all the addresses in use.

- 2. *Leader based* protocols, in which a single node keeps a definitive record of every address in use.

- 3. *Hybrid* protocols, where every node possesses a subset of the total address space, which it can allocate parts of to other nodes.

#### 2.2.1.4 <u>Terminology</u>

Here are definitions of the terms to describe node operations and states in this work.

- 1. Requesting Node: The node which wishes to join a network

- 2. Attachment Agent / Initiator node: The node which is responsible for requesting an address on behalf of the Requesting Node.

- 3. Address request (AREQ): the message broadcast to the network to enquire if the candidate address is unique

- 4. Address reply (AREP): the message unicast back to the requesting node informing whether the address is unique

#### 2.2.2 Decentralised Protocols

In decentralised protocols, no one node has a definitive list of every address in use throughout the network, so there must be a decentralised method of allocating unique addresses.

Most decentralised protocols rely on some form of *Duplicate Address Detection* (DAD). In the simplest form of DAD, the requesting node randomly selects a tentative network address, and broadcasts an *address request (AREQ)* message to determine if the address is already in use. Nodes which receive the AREQ may issue an *address reply (AREP)* message to indicate that the address is already in use. Such an approach is employed in *IPv4 Link-Local Dynamic Address Allocation (ZeroConf*) [21]. However, there are a number of problems with applying this approach to ad hoc networks, which shall be discussed in the following sections.

#### 2.2.2.1 <u>Routing To Uninitialised Nodes</u>

The ZeroConf protocol is only applicable to link-local networks, i.e. all the nodes in the network are totally connected by physical or logical links, thus AREP messages can be reliably delivered to the requesting node. However, in a multi-hop ad-hoc network, if the tentative address is not unique, AREP messages may not be correctly routed.

Perkins et al. [22] propose a scheme which attempts to reduce the probability of this event. In addition to selecting a candidate address, requesting nodes select a temporary source address from an address range reserved for this process, thus guaranteeing that the source address will not be in use by any existing nodes. However, there still exists the small possibility that two requesting nodes may simultaneously select the same temporary source address, in which case AREP messages may not be correctly routed [23, 24].

The protocols proposed in [20, 24] solve this problem by using an *attachment agent* to perform the duplicate address detection on behalf of the requesting node. The attachment agent is already has a unique address, thus the network can reliably route AREP messages to it. The attachment agent and the requesting node can reliably exchange messages, as they have share a direct link.

#### 2.2.2.2 Limited Address Space

It can be observed that for simple DAD to perform efficiently, the ratio between the size of the available address space and the size of the network must be quite large. In [21, 22] the 169.254/16 address range (approx. 65,000 addresses) is reserved for this purpose, giving a host joining a network comprising 1300 hosts a 98% chance of selecting an unused address on its first attempt [21]. However, bandwidth is a very limited resource in ad hoc sensor networks [25], thus it is desirable to conserve bandwidth by reducing the address length and thus the addressing overhead.

In MANETconf [24], each node maintains a record of the addresses it knows to be in use, allowing the attachment agent to select an address which has a high probability of being unused. All nodes which receive the AREQ from the attachment agent, must acknowledge it; this enables the attachment agent to release addresses which it does not receive replies from, providing a mechanism to detect crashed nodes. Together, these features make MANETconf applicable to networks with a limited address space. In fact, it restricts usage to networks with a limited address space, as every node must have sufficient memory to store the address of every node in the network.

Boleng [20] proposes a variable length addressing scheme in which the address space grows with the size of the network. All nodes maintain two addressing parameters: ADDR\_LEN, the current address length in use, and HIGH\_ADDR, the highest address in use. This allows addresses to be allocated sequentially instead of randomly. However, the maintenance of these parameters adds overhead to the network, especially when the address space is incremented. Furthermore, the protocol does not provide a mechanism to recover addresses from crashed nodes.

#### 2.2.2.3 <u>Unbounded Delays</u>

Nesargi and Prakash [24] discuss the importance of selecting timeout periods for DAD attempts. The timeout period is a compromise between timely address allocation, and the chance of failing to detect duplicate addresses too far away from the requesting node. The authors state that to ensure that all duplicate addresses are detected, the timeout period must be a function of the diameter of the network, which in the worst case can be O(n), where *n* is the number of nodes.

Furthermore, Vaidya [26] presents the following theorem:

"Strong DAD cannot be guaranteed if message delays between at least one pair of nodes in the network are unbounded."

In a sparse outdoor ad hoc network, partitions due to weather conditions or node failures may result unbounded message delays, thus causing DAD to fail. Considering that such partitions are usually temporary, the resulting message delays could be considered bounded, but the timeouts required to ensure success are impractically long.

MANETconf addresses this issue by maintaining state information, i.e. each node has a list of all the addresses it knows to be in use. If the initiator node receives affirmative AREP messages from all the addresses in its list, it can be fairly certain that the candidate address is not in use without waiting for the timeout to expire.

#### 2.2.2.4 Control Overhead

As previously mentioned, bandwidth is a very limited resource in ad hoc sensor networks [25]. Every DAD based protocol discussed so far have one common disadvantage – each address allocation operation requires the network to be flooded with an AREQ message, thus a non-trivial amount of bandwidth is consumed each time a node joins. In particular, MANETconf [24] requires all nodes to unicast AREP messages in reply to a AREQ message. The amount of bandwidth consumed is related to the size of the network, thus the scalability of these approaches is generally poor. This is an intrinsic disadvantage of distributed DAD based approaches, and there is little that can be done to mitigate it without introducing some sort of centralisation. Sun and Belding-Royer propose such a scheme which combines DAD and centralisation [27], which shall be discussed in the following section.

#### 2.2.3 Leader-based Protocols

Leader-based protocols employ a single node to maintain a definitive list of addresses in use throughout the network. This node may perform two functions:

- 1. Verify the uniqueness of a node's tentative address.

- 2. Directly allocate unique addresses to nodes.

The classic example of a leader-based protocol is the *dynamic host configuration protocol* (DHCP) [28], a client-server based protocol for automatic configuration of clients in TCP/IP networks. The protocol includes a dynamic address allocation mechanism, in which the DHCP server allocates addresses to clients on a renewable time-limited lease. If the client allows the lease to expire, the address will be made available for allocation to other clients, allowing addresses to be reused without being explicitly released by the client.

However, ad hoc networks are by definition devoid of static infrastructure, precluding the use of DHCP in its traditional form. The leader-based protocols researched [27, 29] all elect a leader from amongst the nodes which form the network. These protocols are discussed further in the following sections.

#### 2.2.3.1 Dynamic Address Configuration Protocol (DACP)

Sun and Belding-Royer [27] propose a protocol based on [22] which combines DAD and a centralised *Address Authority (AA)*. (This protocol is referred to by the same authors in [17] as *DACP*). The first and second nodes to join the network respectively assume the roles of *Primary Address Authority (PAA)*, and the redundant *Backup Address Authority (BAA)*.

The PAA periodically broadcasts a beacon message, advertising its presence to the network. A node may detect a network partition if it stops receiving beacon messages from the PAA, in which case a new PAA is elected for the partitioned network. If the BAA is inside the partitioned network, it may automatically take over as the PAA. Conversely, a node may detect a network merge if it receives beacon messages from two different PAAs, in which case the two PAAs will exchange address lists and eliminate and reallocate duplicate addresses.

A requesting node selects a candidate address and a temporary sources address, and performs DAD in an identical manner to that described in [22]. If a duplicate address exists, either the node possessing the duplicated address or the PAA may reply with an AREP message, which allows for faster detection of duplicate addresses. However, there is no mechanism to speed up confirmation that the candidate address is unique.

Once the requesting node is satisfied that its candidate address is unique, it registers its address and requested lease duration with the PAA. The lease mechanism is identical to that used in DHCP [28], allowing an address to be released if the node does not renew its lease, whilst allowing temporarily disconnected nodes to retain their addresses.

The authors also argue that because routing information is accumulated by the AREQ messages, the AREP message can be routed back to the correct recipient even if two requesting nodes are concurrently using the same temporary source address. However, they do not consider the case where the two requesting nodes share an identical route, which has a reasonable probability in very small networks.

#### 2.2.3.2 Optimised DACP (ODACP)

Sun and Belding-Royer propose in [17] an optimised version of their DACP protocol sans DAD and the associated overhead, resulting in a pure leader-based scheme. Instead of flooding the network with AREQ messages, the requesting node unicasts the AREQ message to the PAA.

#### 2.2.3.3 Dynamic Address Allocation Protocol (DAAP)

Patchipulusu [30] proposes a scheme in which the last node to join the network takes on the responsibility of being the leader. Addresses are assigned sequentially, and all nodes keep a record of the highest address in use (the address of the leader). All nodes periodically broadcast "hello" messages containing a network identifier, which facilitates the detection of network merges and partitions.

#### 2.2.4 Hybrid Protocols

In a hybrid protocol, every node is a leader with the authority to allocate addresses from a subset of the address space.

# 2.2.4.1 <u>Nigel Sim's Solution</u>

Nigel Sim [1] proposes a scheme based on a binary tree, where each node has the authority to assign two child addresses, which consist of a single bit appended to the parent's address. This concept has the advantage of variable address length. However, this scheme does not consider the case where a requesting node is unable to establish a direct link to a parent which has not already assigned both its child addresses, nor does it consider the topology of the network. Consider the best case scenario, where the topology of the network is a complete binary tree. The required address length would be  $log_2 n$ , i.e. there would be few wasted addresses. However, consider the worst case scenario, where the network has a linear topology, which would require *n* bit long addresses, i.e. there would be  $2^n - n$  wasted addresses. This scheme is clearly only suitable for dense networks where the topology remains static for the lifetime of the network. However, [23, 31] (which are discussed below) make use of this concept of each node having authority over a subset of the address space resulting in low maintenance addressing schemes with little overhead.

#### 2.2.4.2 Address Pool Protocols

Both Tayal and Patnaik [23] and Hu and Li [31] have presented protocols based on the address pool concept. Instead of a single address, each node is allocated a set of addresses, the first address of which it uses for itself. Upon request, it will relinquish part of its address pool to a requesting node. This operation does not require multi-hop routing or distributed agreement, thus mitigating the disadvantages common to other protocols such as flooding messages, non-trivial timeouts and delays, protocol modifications, overhead of periodical maintenance messages, and major address leaks [31]. Another major advantage is that partitioning and subsequent remerging of a network need not incur any control overhead. The two hybrid protocols reviewed here differ primarily in their solution to the address depletion problem, where a joining node is not in range of an existing node which possesses an available address.

# 2.2.4.3 ZAL: Zero-Maintenance Address Allocation

*ZAL* [31] takes a proactive approach to the address depletion problem, using the *ZAL Distribution Equalization (ZAL/DE)* algorithm. *ZAL/DE* promotes even distribution of addresses throughout the network by attempting to ensure there are a predetermined number of available addresses within transmission range of any node in the network. Nodes which possess surplus addresses will attempt to distribute them to other nodes. However, this process will only occur when absolutely necessary to maintain the minimum number of available addresses in an area, thus there is no control overhead in a stable network.

In the event that a requesting node cannot obtain an address from any of its immediate neighbours, it randomly selects a temporary address from a reserved address range until it can obtain a permanent unique address. However, this assumes the node is mobile, and will eventually come into direct contact with a node which has an available address. This obviously will not work for a sensor network in which all the nodes are static. Furthermore, this solution does not provide a mechanism to reclaim leaked addresses.

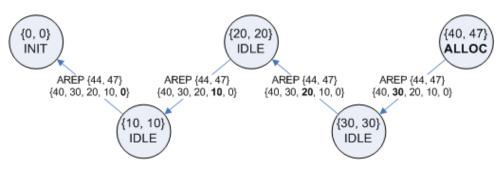

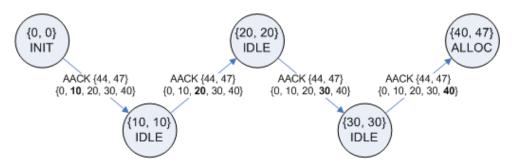

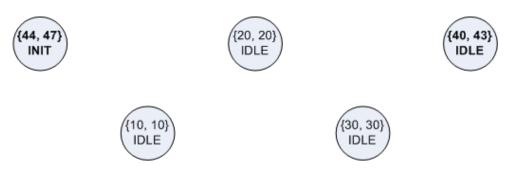

# 2.2.4.4 The Tayal and Patnaik solution

The solution proposed by Tayal and Patnaik [23] takes a reactive approach to the address depletion problem. When a requesting node cannot contact a node that has available addresses, the attachment agent floods the network with a request for an available address pool. This process also provides a mechanism to reclaim leaked addresses; any nodes which no not respond to the address request within a bounded timeframe can have their address pools reclaimed. Any reclaimed address pools are always repossessed by a node which contains an adjacent address block. This eases the memory requirements on the nodes, as the address pools will always be a contiguous block, which can be defined by its start and end addresses.

#### 2.2.5 Discussion

To determine the best approach to the address allocation problem for this project, it is worthwhile to consider the most likely deployment situation for this type of network.

The network will most likely be deployed outdoors, with a distance between the nodes of up to 10km. Most of the nodes will be deployed when the network is initially set up, and additional nodes may be added or removed throughout the life of the network. Nodes may crash as their batteries fail, or due to equipment failure. Weather conditions may temporarily affect the link quality, potentially causing temporary network partitions and subsequent remerges. Other devices operating in the same ISM band may cause interference, which may interfere with the operation of one or more nodes, potentially causing temporary network partitions.

A key point here is that most network partitions will be temporary. Whilst the network partitions must be able to continue operating until they are remerged, it is a potential waste of energy to establish new network infrastructure for each partition if they are inevitably, going to be remerged. The hybrid protocol concept is very suitable in this respect, as there is no control overhead for a network partition and subsequent remerging.

The salient feature of the Tayal and Patnaik solution [23] is its simplicity, and that all operations remain local unless address depletion occurs. The principle of contiguous address spaces is very desirable, as it eases memory requirements, and reduces the bandwidth required for nodes to exchange address spaces.

The other impressive feature of ZAL [31] is that it proactively ensures even distribution of addresses throughout the network. The authors claim that the network requires zero maintenance once it has reached a stable state, however reaching a stable state comes with a non-trivial energy cost, particularly in a sparse network.

However, ZAL does have some passive features which promote even distribution of addresses. For example, a requesting node does not accept the first address offer it receives. Instead, it waits for all replies to arrive, then accepts the largest offer. This increases the time it takes to obtain an address, but it does not make the operation any more energy expensive.

A potential area in which the Tayal and Patnaik protocol can be improved is the method used to search the network for available addresses. The authors specify that if a node receives an address request but does not possess any available addresses, it immediately floods the network with an address search message. Therefore, even if other nodes which received the address request are able to provide addresses to the requesting node, this message will be flooded to the network. This method could be improved to only propagate the search message when it is absolutely necessary, thereby conserving energy.

#### 2.2.6 Conclusions

It is clear that the address allocation protocol for this project should be based on the hybrid protocols [23, 31], primarily because of their ability to deal with temporary network partitions, and low control overhead. The protocol to be developed will attempt to incorporate the salient features of both protocols, as well as adaptations to conserve energy in a sparse long range network. The operation of this protocol is discussed further in section 3.5 (p. 60).

# Chapter 3

# DEVELOPMENT

# **3.1 HARDWARE ARCHITECTURE**

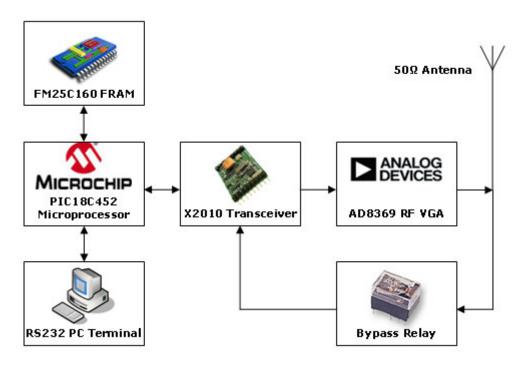

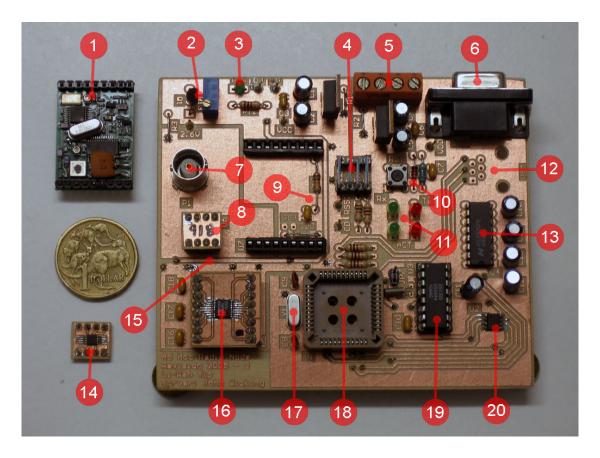

The hardware platform previously designed by Sloots [2] worked successfully, and as such will only be subject to minor improvements, the main goal of which will be decreasing power consumption. A block diagram of the 2004 hardware platform is shown below in Figure 3.1.

#### 3.1.1 VGA Bypass Problem

As can be seen in Figure 3.1, an X2010 transceiver module is used in conjunction with an AD8369 Variable gain amplifier (VGA) to provide programmable output power, as required to implement the power aware routing extension developed in 2004. The transceiver only has one antenna connection; hence a relay provides a return signal path around the VGA to allow reception. This was an improvised solution, and as a result is far from ideal:

- The relay contact closing time causes an additional delay when switching between receive and transmit modes. This delay was found to be between 5 and 15 milliseconds [2], which exceeds the X2010 transceiver's inherent switching delay of 5 milliseconds.

- The current required to reliably latch the relay contacts is typically 550mA, which the microprocessor must drive via a switching transistor [2]. More importantly, this incurs a power consumption of 2.75W<sup>1</sup>, which is clearly unacceptable in an application where power conservation is an important criterion.

Several solutions to this problem were considered. One option was to retain the same configuration, but use a low power relay. The lowest power relay available through Farnell InOne is the NEC EF2 ultra low power relay [32], which has a power consumption of 50mW, and an operation time of 4ms. However the device is expensive, costing \$14.51 (AUD) for a single unit.

A second option was to eliminate the bypass relay by using separate transmitter and receiver modules, which allows for two separate antennae. However, this would increase the size and cost of each node.

<sup>&</sup>lt;sup>1</sup> Power consumption is based on a power supply of 5 Volts DC.

A third option was to use a transceiver module with programmable output power. The LPRS ER400TRS "Easy Radio" transceiver module [33] features programmable output power, frequency, and data rate, and handles low level functions such as Manchester encoding and buffering. This would eliminate the bypass relay, the AD8369 VGA, and the software Manchester encoder/decoder. Unfortunately, the maximum output power for the device is only 10mW. To maximise communications range, the nodes should be able to transmit at the maximum allowable power for licence free transmission, which for the Australian 433 MHz band is 25 mW. If this device were available with a higher transmission power, it would be the ideal solution.

The chosen solution was to replace the relay with a solid state CMOS switch, which is far smaller and consumes an insignificant amount of power. General purpose CMOS switches are unsuitable for switching high frequency signals due to impedance problems. However, Analog Devices produces a range of wideband analogue switches specially designed for RF applications (ADG918/919, [34]). These devices provide low insertion loss in the 'ON' state and high port separation in the 'OFF' state at frequencies up to 1 GHz, and have very low power consumption (~1uA). Unfortunately, the devices only operate over 1.65V - 2.75V, and will hence require a separate power supply.

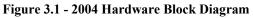

A suitable power supply for a low current device is an emitter-follower voltage source. Sources of this type would typically use a Zener diode to provide a reference voltage (Figure 3.2a). However, to operate a Zener diode in its Zener region requires approximately 10mA of current, which is not acceptable overhead for this application. The alternative is to use a resistor voltage divider to provide the reference voltage (Figure 3.2b). Achieving a precise ratio with discrete resistors is difficult at best, thus a trimmer potentiometer will be used in the prototype allowing the voltage to be tuned to the correct level.

a) Zener diode as reference b) Resistor voltage divider as reference Figure 3.2 - Emitter Follower Voltage Sources

#### 3.1.2 New Hardware Requirements

#### 3.1.2.1 <u>Real Time Clock</u>

A real time clock is to be included in this hardware design for several reasons:

- 1. To enable accurate scheduling of data sampling.

- 2. To allow data samples to be time stamped.

- 3. To allow accurate timing of sleep-wakeup schedules.

The RTC device should feature programmable alarms that are capable of generating hardware interrupts for the PIC microcontroller. A suitable device was found in the Maxim-Dallas DS1305 Serial Real Time Clock [35], which features two programmable alarms with separate interrupt lines, and a SPI interface.

# **3.2 SOFTWARE ARCHITECTURE**

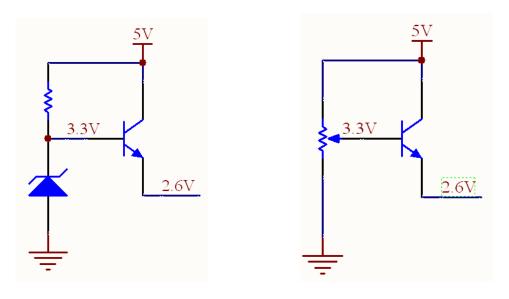

#### 3.2.1 The OSI Model

The *Open Systems Interconnect Model* (OSI Model) divides the functions of a communication system into 7 layers of abstraction. This model allows a communication system to be designed as a 'stack' of protocols, each of which implement the functionality of a layer.

Figure 3.3 - The 7 Layers of the OSI Model [36]

The key concept of the OSI Model is encapsulation, which defines the way in which the layers interact with each other. Each layer is only dependent on the functionality of the layer immediately below it, and only provides functionality to the layer immediately above it.

The protocol layers in different devices communicate with each other using a *Protocol Data Unit* (PDU), which comprises a header containing information specific to that protocol layer, and a data section which encapsulates the PDU of the next higher layer. The header is removed before the PDU is passed up to the next higher layer, so a particular layer will only ever see its own PDU. This allows a communications system to encompass many devices using different communications protocols and transmission media.

This thesis project is only concerned with developing a network access module, which comprises the first three layers of the OSI Model. The descriptions of these layers according to Wikipedia [36] are given below.

#### 3.2.1.1 <u>Physical Layer</u>

The physical layer defines and implements the mechanical and electrical interface between devices. Its primary function is to convert the data as it is represented within the device into a signal suitable for the communication medium, i.e. an electrical, light, or radio signal, and to convert it back at the receiver.

Important aspects of the physical layer for a radio based system include:

- 1. Transceiver hardware.

- 2. Transmission frequency.

- 3. Baud rate.

- 4. Encoding at the transmitter, and decoding and synchronisation at the receiver.

- 5. Establishment and termination of transmissions.

#### 3.2.1.2 Data Link Layer

The data link layer ensures the reliable transmission of frames between two devices which share a point-to-point link. The data link layer is further divided into two sublayers: the Media Access Control (MAC) layer, and the Logical Link Control (LLC) layer.

#### 3.2.1.2.1 Media Access Control Layer

The MAC layer converts the raw bit stream received by the physical layer into frames, which are the data link layer PDU. This includes:

- 1. Delimiting the frames at the transmitter, and extracting frames from the bit stream at the receiver.

- 2. MAC Addresses, filtering frames not intended for the device.

- 3. Calculation, appending, and verification of the CRC.

4. Controlling access to the media i.e. Carrier Sense Multiple Access (CSMA).

#### 3.2.1.2.2 Logical Link Control Layer

The LLC layer is responsible for converting between network layer packets and data link layer frames. This includes:

- 1. Fragmenting network layer packets which are too large into smaller MAC layer frames, and reassembling them at the receiver. (Type 1, 2, 3)

- 2. Ensuring reliable point-to-point delivery of frames. (Type 2, 3)

- 3. Reassembling frames in the correct order. (Type 2)

The LLC layer is not implemented in this project.

#### 3.2.1.3 <u>Network Layer</u>

The network layer is responsible for conveying a message between any two nodes in the network. This includes:

- 1. Global network layer addressing.

- 2. Dynamic address allocation.

- 3. Resolving network layer addresses to MAC layer addresses.

- 4. Routing.

#### 3.2.2 Relocatable Code

Assembly language programs for Microchip PIC microprocessors are traditionally compiled as absolute code, meaning that the executable code is generated directly from a single monolithic source file, and program and data memory addresses are assigned at compile time.

The software developed by Steven Sloots was written in this manner, with the source file containing over three 3000 lines of code, 120 cryptic variables, and 350 code labels and constants. This made the code very difficult to understand and work with, and was exacerbated by a lack of comprehensive commenting and documentation.

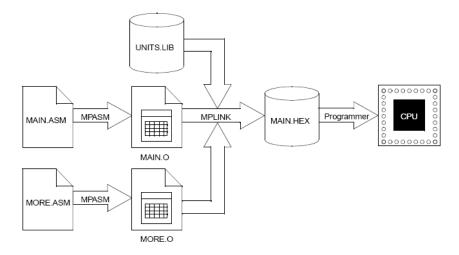

The introduction of MPASM v2.00 and MPLINK v1.00 [37] allows the generation of *relocatable code*, meaning that several source files are compiled into individual object modules. These object modules are then combined by a linker to generate executable code (Figure 3.4). This has several advantages over absolute code generation:

- 1. The program can be split into several independent and reusable code modules.

- 2. Each module has a separate namespace for program and data memory labels.

- 3. Only the affected modules need to be recompiled when changes to the program are made.

Figure 3.4 - Generating Executable Code from Object Modules [37]

The software will be redeveloped for this project using relocatable code, with these specific objectives:

- 1. Make the code modular, reusable, and easy to understand.

- 2. Limit the scope of each code module to a single protocol, so that each protocol can be worked on independently.

- 3. Create a well defined interface for each code module, to promote encapsulation and reusability.

- 4. Consistent standard of comprehensive commenting, especially for each subroutine / code block (not just line-by-line comments).

- 5. Create comprehensive documentation in the form of module interaction diagrams and flow charts.

- 6. Allow the code to be easily extended in future projects.

# 3.3 MANCHESTER ENCODING AND DECODING

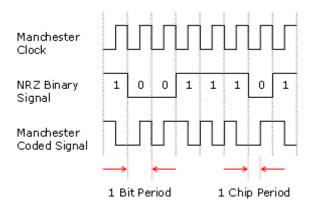

As stated earlier, the X2010 radio transceiver is AC coupled on its data pins, thus the data must be Manchester encoded to ensure that there is no DC component in the transmitted bit stream. This introduces the need for the following functions: